Фінансові новини

- |

- 17.05.24

- |

- 14:35

- |

-

RSS

RSS - |

- мапа сайту

Авторизация

Чипи TSMC розміром 120 x 120 мм з'являться завдяки новій технології CoWoS

10:01 30.04.2024 |

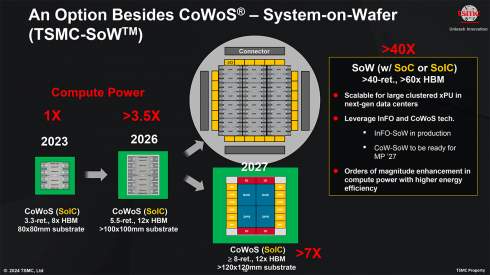

Рекорд з найбільшого розміру чипа звучить як щось сумнівне, але не у випадку TSMC. Компанія представила технологією пакування чип-на-пластині-на-підкладці (CoWoS), яка дозволить створити системи-у-пакуванні (SiP), у рази більші від наявних процесорів NVIDIA B200 або AMD Instinct MI300X. Процесори матимуть монструозні розміри 120 х 120 мм та споживатимуть кіловати енергії.

«CoWoS®, SoIC і System-on-Wafer (TSMC-SoWTM): мікросхема TSMC на-пластині-на-підкладці (CoWoS) стала ключовим фактором революції штучного інтелекту, дозволяючи клієнтам використовувати більше ядер процесора та пам'ять із високою пропускною здатністю (HBM), укладаються поруч на один проміжний пристрій. Водночас наша система на інтегрованих мікросхемах (SoIC) зарекомендувала себе як провідне рішення для стекування 3D-чипів, і клієнти все частіше поєднують CoWoS із SoIC та іншими компонентами для максимальної інтеграції системи в пакет (SiP)

Завдяки System-on-Wafer компанія TSMC пропонує нову революційну опцію, яка дозволяє використовувати великий масив матриць на 300-мм пластині, пропонуючи більшу обчислювальну потужність, займаючи набагато менше місця в центрі обробки даних і підвищуючи продуктивність на ват на порядки. Перша пропозиція TSMC SoW, пластина з логічною схемою, заснована на технології Integrated Fan-Out (InFO), вже у виробництві. Версія chip-on-wafer, що використовує технологію CoWoS, запланована на 2027 рік, що дозволить інтегрувати SoIC, HBM та інші компоненти для створення потужної системи на рівні пластини з обчислювальною потужністю, порівнянною з серверною стійкою центру обробки даних або навіть з цілим сервером».

Платформа використовує раніше розроблену компанією технологію InFO_SoW, яка дозволяє створювати чипи великих розмірів, а також технологію System on Integrated Chips (SoIC). Інша технологія, Chip-on-Wafer (CoW) дозволяє розміщувати поверх системи пам'ять або інші елементи.

Фактично йдеться про процесори, порівнянні за розміром з цілою 300 мм кремнієвою платиною, які дозволять розміщувати величезну кількість ядер. Подібний метод пакування ядер забезпечить підвищення продуктивності та енергоефективності за допомогою високих швидкостей між компонентами. Всередині система матиме низькі затримки між ядрами та низький спротив під час передавання енергії. На відміну від попередніх технологій, CoWoS дозволяє використовувати у компонуванні чипа різні техпроцеси та швидкісну пам'ять HBM4.

ТЕГИ

ТОП-НОВИНИ

ПІДПИСКА НА НОВИНИ

Для підписки на розсилку новин введіть Вашу поштову адресу :

За даними слідства, через своє підприємство та службових осіб

Міністерства енергетики та Державної податкової служби він завдав

державі шкоди на понад 2 млрд грн на махінаціях у вугільній сфері.

За даними слідства, через своє підприємство та службових осіб

Міністерства енергетики та Державної податкової служби він завдав

державі шкоди на понад 2 млрд грн на махінаціях у вугільній сфері. У російському місті Туапсе (Краснодарський край) через сьогоднішню атаку

безпілотників сталася пожежа на місцевому нафтопереробному заводі.

У російському місті Туапсе (Краснодарський край) через сьогоднішню атаку

безпілотників сталася пожежа на місцевому нафтопереробному заводі. В мережі повідомляють, що окрім порту у Новоросійську також

було завдано удару безпілотниками по нафтобазі та залізничній станції у

Краснодарському краї.

В мережі повідомляють, що окрім порту у Новоросійську також

було завдано удару безпілотниками по нафтобазі та залізничній станції у

Краснодарському краї. Союзники по НАТО поступово наближаються до рішення відправити в Україну

свої війська. Їх використовуватимуть для навчання українських сил.

Союзники по НАТО поступово наближаються до рішення відправити в Україну

свої війська. Їх використовуватимуть для навчання українських сил. Українські посадовці, відповідаючи на запити щодо їхнього елітного майна в ОАЕ, заявили, що «нічого про це не знають».

Українські посадовці, відповідаючи на запити щодо їхнього елітного майна в ОАЕ, заявили, що «нічого про це не знають». У програмі можуть взяти участь фізичні та юридичні особи, які

здійснюють господарську діяльність з виробництва повітряних і космічних

літальних апаратів, супутнього обладнання та здійснюють виробництво БпЛА

або їх частин (за КВЕД 30.30).

У програмі можуть взяти участь фізичні та юридичні особи, які

здійснюють господарську діяльність з виробництва повітряних і космічних

літальних апаратів, супутнього обладнання та здійснюють виробництво БпЛА

або їх частин (за КВЕД 30.30). Конвенція, що відкрита для приєднання також для країн за межами

Європи, охоплює усі аспекти застосування і ризиків, пов'язаних із

застосуванням ШІ в контексті дотримання прав людини, поваги до

демократичних стандартів і верховенства права.

Конвенція, що відкрита для приєднання також для країн за межами

Європи, охоплює усі аспекти застосування і ризиків, пов'язаних із

застосуванням ШІ в контексті дотримання прав людини, поваги до

демократичних стандартів і верховенства права.  Intel оголосила про запуск нової програми з назвою Thunderbolt Share,

яка революціонізує спосіб взаємодії між комп'ютерами. Ця інноваційна

технологія дозволяє двом ПК працювати як один, спільно використовуючи

мишу, клавіатуру, екрани, пам'ять та інші ресурси.

Intel оголосила про запуск нової програми з назвою Thunderbolt Share,

яка революціонізує спосіб взаємодії між комп'ютерами. Ця інноваційна

технологія дозволяє двом ПК працювати як один, спільно використовуючи

мишу, клавіатуру, екрани, пам'ять та інші ресурси. TikTok у тестовому режимі запустив можливість завантаження довгих відео

тривалістю до 60 хвилин. Поки що функція тестується на обмеженій

кількості користувачів і невідомо коли стане доступною усім і чи стане

взагалі.

TikTok у тестовому режимі запустив можливість завантаження довгих відео

тривалістю до 60 хвилин. Поки що функція тестується на обмеженій

кількості користувачів і невідомо коли стане доступною усім і чи стане

взагалі. Google Play Protect представляє нову функцію Live Threat Detection, яка

використовує штучний інтелект для аналізу використання чутливих дозволів

і взаємодії з іншими додатками та послугами.

Google Play Protect представляє нову функцію Live Threat Detection, яка

використовує штучний інтелект для аналізу використання чутливих дозволів

і взаємодії з іншими додатками та послугами. У новій версії операційної системи Android 15, розробники впровадили

штучний інтелект для виявлення крадіжок. Ця функція дає змогу пристрою

визначити незвичайні або підозрілі дії, які можуть вказувати на спробу

крадіжки.

У новій версії операційної системи Android 15, розробники впровадили

штучний інтелект для виявлення крадіжок. Ця функція дає змогу пристрою

визначити незвичайні або підозрілі дії, які можуть вказувати на спробу

крадіжки. Південнокорейська марка Kia оновила екстер'єр та інтер'єр електричного кросовера EV6, додавши більше потужності та технологій.

Південнокорейська марка Kia оновила екстер'єр та інтер'єр електричного кросовера EV6, додавши більше потужності та технологій. Apple анонсувала низку нових функцій, які стануть доступними у iOS 18,

iPadOS 18, macOS 15 і visionOS 2 пізніше цього року і полегшать

використання гаджетів людьми з обмеженими можливостями.

Apple анонсувала низку нових функцій, які стануть доступними у iOS 18,

iPadOS 18, macOS 15 і visionOS 2 пізніше цього року і полегшать

використання гаджетів людьми з обмеженими можливостями. Влада Канади заарештувала самопроголошеного «криптокороля» Ейдена

Плетерскі та його партнера за звинуваченням у створенні схеми Понці.

Згідно із заявою Комісії з цінних паперів Онтаріо (OSC), їх підозрюють у

шахрайстві на $30 млн.

Влада Канади заарештувала самопроголошеного «криптокороля» Ейдена

Плетерскі та його партнера за звинуваченням у створенні схеми Понці.

Згідно із заявою Комісії з цінних паперів Онтаріо (OSC), їх підозрюють у

шахрайстві на $30 млн. Microsoft просить деяких своїх співробітників, які працюють у Китаї,

розглянути можливість переїзду за межі країни, оскільки відносини між

США і КНР стають все більш напруженими через технології штучного

інтелекту і напівпровідників.

Microsoft просить деяких своїх співробітників, які працюють у Китаї,

розглянути можливість переїзду за межі країни, оскільки відносини між

США і КНР стають все більш напруженими через технології штучного

інтелекту і напівпровідників. Говорячи про Astra, CEO експериментальної лабораторії DeepMind, Деміс

Хассабіс розповів, що його команда завжди хотіла розробити

універсального агента ШІ, який був би корисними у повсякденному житті.

Говорячи про Astra, CEO експериментальної лабораторії DeepMind, Деміс

Хассабіс розповів, що його команда завжди хотіла розробити

універсального агента ШІ, який був би корисними у повсякденному житті. Проте компанія не припинить експериментувати з іншими ідеями:

наприклад, пізніше цього року у продаж має надійти прозорий бездротовий

телевізор LG OLED T.

Проте компанія не припинить експериментувати з іншими ідеями:

наприклад, пізніше цього року у продаж має надійти прозорий бездротовий

телевізор LG OLED T. Хакери з Північної Кореї вкрали 147,5 млн доларів у криптовалюті з біржі

HTX наприкінці 2023 року, а потім відмили їх через платформу Tornado

Cash у березні 2024 року.

Хакери з Північної Кореї вкрали 147,5 млн доларів у криптовалюті з біржі

HTX наприкінці 2023 року, а потім відмили їх через платформу Tornado

Cash у березні 2024 року. Штучний інтелект створюватиме малюнки, відео і музику, а також попереджатиме про телефонних шахраїв.

Штучний інтелект створюватиме малюнки, відео і музику, а також попереджатиме про телефонних шахраїв. Google DeepMind представила на Google I/O вдосконалену версію своєї

моделі штучного інтелекту, яка прогнозує не лише структуру білків, але й

структуру «всіх молекул життя».

Google DeepMind представила на Google I/O вдосконалену версію своєї

моделі штучного інтелекту, яка прогнозує не лише структуру білків, але й

структуру «всіх молекул життя».